Global Service

Three-dimensional integrated circuits (3DICs) have emerged as a promising solution to meet the increasing demands for high performance and compactness in modern applications. By stacking individual ICs/wafers together as a single package, 3DIC technology offers several advantages over traditional two-dimensional (2D) integrated circuits.

The evolution of semiconductor technologies into sub-10 nm nodes and 3D architectures like high-bandwidth memory (HBM), even small static potentials can result in critical device failures. The effectiveness of DC ionization compared to AC systems, especially for protecting advanced packaging structures such as micro-bumps and TSVs. As semiconductor processes scale down and packaging grows more complex, controlling ESD during wet cleaning and drying becomes essential.

Test wafers play an indispensable role in the semiconductor industry, fulfilling various functions that are vital for manufacturing, failure analysis and quality assurance of semiconductor devices. Test wafers are of paramount importance in ensuring the reliability and efficiency of semiconductor devices and technologies.

Handling ultrathin wafers and reducing wafer thickness without damaging the pre-process has been a challenging task for semiconductor industries. Temporary bonding and debonding (TBDB) technology was developed to address this.

In semiconductor manufacturing, dicing or singulation is a critical process that separates individual dies from a processed wafer. Whether performed mechanically or with lasers, this step introduces significant physical stress on the wafer, which may lead to chipping or cracking of the silicon (Si) substrate.

Handling and processing thin wafers mounted on a frame post-debonding, along with the subsequent cleaning process, presents formidable challenges in advanced semiconductor packaging technologies. Conventional cleaning methods carry the risk of damaging thinned wafers.

In modern semiconductor process, removing the photoresist is a critical step. After the lithography process, the exposed photoresist must be removed from the wafer surface to reveal the patterned areas for further processing.

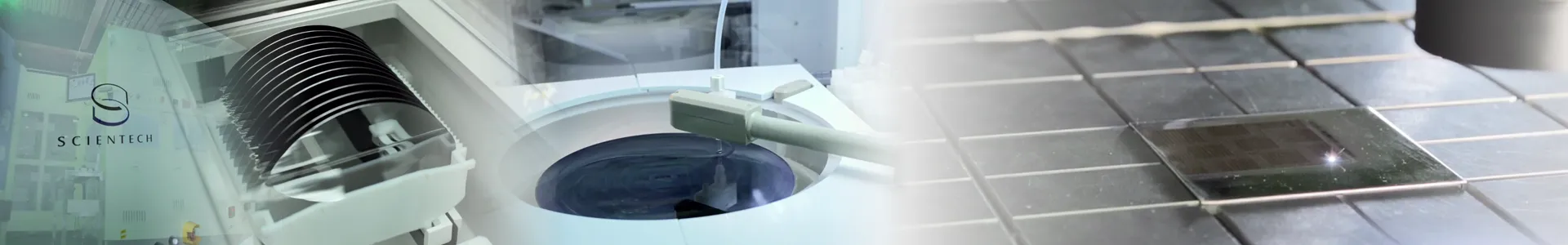

Scientech’s wet process equipment has been successfully implemented in the fabrication of the recent chipset 3DIC, CoWoS and advanced packaging process.

The semiconductor industry is undergoing a profound transformation as devices demand higher performance, smaller form factors, and lower power consumption. Traditional packaging approaches are no longer sufficient to meet the requirements of AI accelerators, high-performance computing (HPC), 5G communication, autonomous vehicles, and consumer electronics, all of which rely heavily on advanced packaging technologies to enable higher bandwidth, greater interconnect density, and improved thermal management.

Wafer warpage is a critical challenge in advanced semiconductor processes, particularly with thin wafers, heterogeneous integration. Warpage can lead to misalignment, transfer failures, and significant yield loss. To tackle these challenges, Scientech together with AMC has developed an integrated solution tailored to modern manufacturing demands.