一、引言

微凸塊(Micro bump)是先進封裝技術中的關鍵微小焊接接點,尺寸通常低於 40 μm,甚至縮小至 10–20 μm,比傳統 BGA(直徑大於 500 μm)或 Flip Chip Bump(直徑約 80–120 μm)小很多,用於實現晶片與晶片(Die-to-Die)或晶片與中介層(Die-to-interposer)之間的高密度連接。

隨著晶片功能複雜度提高與摩爾定律(Moore's Law)面臨物理極限,半導體產業的重心已從單純的「電晶體縮微」轉向「封裝技術的創新」,產業逐漸由單晶片系統(SoC)轉向小晶片(Chiplet)與異質整合架構。為實現晶片與晶片之間的高密度互連,微凸塊(Micro bump)技術被廣泛應用在 2.5D / 3D 及小晶片(Chiplet)封裝。

二、微凸塊(Micro bump)結構

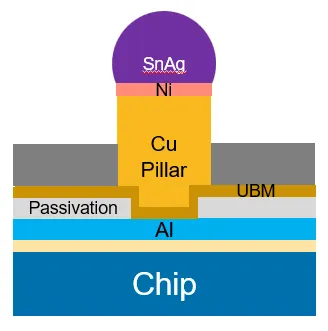

可能搭配 underfill 增強可靠度,微凸塊(Micro bump)通常由以下幾層構成(由下往上):

- UBM(Under Bump Metallization):通常由鈦(Ti)與銅(Cu)組成,負責增強黏著力並阻擋原子擴散。

- 銅柱(Cu pillar):凸塊的主體,提供優異的導電性與機械支撐,並縮小間距以適應高密度封裝。

- 擴散阻障層 (Barrier Layer):通常為鎳(Ni),防止銅與錫反應過快,產生過厚的脆性介金屬化合物(IMC)。

焊錫帽(SnAg 等):通常為無鉛錫銀合金 (SnAg),在加熱回焊後,與另一個晶片的金屬墊結合。

三、微凸塊(Micro bump)的用途

微凸塊(Micro bump)主要用途是作為晶片與晶片(Die-to-Die)或晶片與中介層(Die-to-Interposer)之間的電性連接與機械支撐。

1. 晶片與晶片間的連接(Die-to-Die Interconnect)

常見於 HBM 記憶體堆疊、Chiplet 架構:

- 提供高密度 I/O

- 縮短訊號傳輸距離

- 降低 RC 延遲與功耗

- 提高資料傳輸頻寬

2. 晶片與中介層(Die-to-Interposer)之間的連接

- 支援不同製程節點晶片整合(Chiplet 架構)

- 連接邏輯晶片、記憶體晶片、類比與射頻模組

四、微凸塊(Micro bump)的主要應用

與傳統 Bump 比較,微凸塊(Micro bump)的特點是高密度、小間距、高 I/O 數量,主要應用如下:

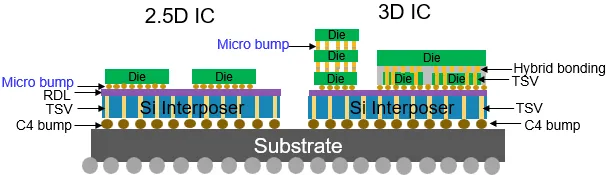

1. 2.5D 封裝(晶片與 Interposer 連接)

- 特點:將多顆晶片放在矽中介層上,提供高密度布線。

- 應用:高效能運算(HPC)、AI 加速器等。

2. 3D IC 垂直堆疊(晶片與晶片連接)

- 功能:搭配 TSV(Through-Silicon Via)進行晶片垂直堆疊,提高整合度與效能,降低封裝面積。

- 應用:HBM 記憶體堆疊、CMOS 影像感測器(CIS)、行動 SoC 晶片等。

3. Chiplet 架構

- 優勢:透過 micro bump 連接不同功能晶片,提升設計彈性、提高良率並降低製造成本。

- 應用:CPU + I/O Die 分離、異質整合(Logic + RF + Analog)、大型 AI 晶片分割設計。

五、微凸塊(Micro bump)挑戰

隨著線寬/間距縮小至 20 μm 以下,微凸塊(Micro bump)技術挑戰愈加明顯:

- 線寬/間距微縮限制:隨著尺寸微縮,錫球縮小會加速金屬化合物(IMC)的生成,造成接點強度下降。

- 電遷移(Electromigration, EM):微小體積內的高電流密度容易導致金屬原子遷移,形成空洞。

- 製程成本與良率:對微影對準精度及電鍍均勻性要求變高,導致設備成本上升,且對缺陷極為敏感。

六、未來發展趨勢

- 尺寸持續微縮:從 40 µm 降至 20 µm,甚至低於 10 µm,以滿足 AI 與 HPC 需求。

- Hybrid Bonding:當間距小於 10 μm 時,將逐漸取代微凸塊。優點包括無焊料接合、更低 RC 延遲與更高密度。

- 銅對銅(Cu-Cu)直接接合:降低接觸電阻,提升訊號完整性,適用於高頻應用。

七、總結

微凸塊(Micro bump)是先進封裝的關鍵技術,實現了晶片與晶片或晶片與中介層之間的高密度連接。雖然面臨尺寸微縮與可靠度挑戰,但在可預見的數年內,微凸塊仍將是先進封裝的主力技術。