隨著摩爾定律(Moore's Law)面臨物理極限,半導體產業的重心已從單純的「電晶體縮微」轉向「封裝技術的創新」。封裝不再只是保護晶片,而是提升效能的關鍵戰場。封裝製程的演進 (Evolution of Packaging Processes)分為以下三階段:

第一階段:傳統封裝 (Traditional Packaging)

傳統封裝技術主要指將單一晶片固定於基板,透過打線(Wire Bonding)或引腳連接,再用塑膠外殼包覆保護。傳統封裝以打線封裝(Wire Bonding)與引腳封裝為主,主要功能是提供電力、散熱及實體保護。

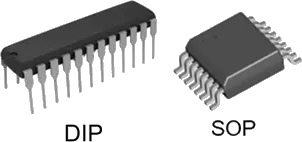

早期: DIP (Dual in-line Package,雙列直插式封裝)、SOP (Small Outline Package, 小外型封裝)。DIP在其兩側有兩排平行的金屬接腳,稱為排針,可插入在DIP插座(socket)上。SOP是一種縮小形式的DIP, 後來逐漸衍生出SOJ(引脚型小外形封裝)、TSOP(薄型小外形封裝)、VSOP(非常小型外形封裝)、SSOP(精簡SOP)、TSSOP(薄型精簡SOP)、SOT(小型外形電晶體)、SOIC(小型外形集成電路)等。

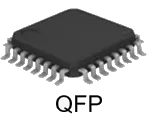

中期: QFP 封裝(Quad Flat Package,四方扁平封裝),開始使用引線框架 (Lead Frame)。QFP是一個表面安裝式包裝,將接腳製作在IC四周,在所有四個側面都有牙齒(L)形狀的銷釘。

後期: BGA (球柵陣列封裝),它使用排列成網格圖案的微小錫球來取代引腳,大幅增加 I/O 數量,並將晶片以錫球方式直接與印刷電路板(PCB)連接。由於引腳(錫球)較短,寄生電感和電容較小,訊號傳輸性能更佳。將晶片直接連接到印刷電路板(PCB) 上,熱量可以有效地從晶片傳導至 PCB,有助於提高系統的穩定性。

第二階段:晶圓級與系統級封裝 (WLP/SiP)

由單顆晶片轉向多功能整合,如晶圓級封裝(WLP)與系統級封裝(SiP),縮小體積並提升訊號傳輸速度。晶圓級封裝(WLP)與系統級封裝(SiP)是現代半導體產業中,實現電子產品輕薄短小與高效能的兩大關鍵封裝技術。

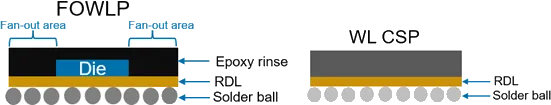

晶圓級封裝 (WLP, Wafer level package): 所謂「晶圓級封裝(Wafer level package)」是指先將整片矽晶圓完成封裝測試後,再進行切割的動作,有效縮小封裝體積。封裝後的體積和晶片本身差不多,是目前封裝體積最小的封裝方式。晶圓級封裝不需要打線 (wire bonding)及導線架(leadframe),透過 RDL 技術將原本分佈在晶片四周的接點重新排列成矩陣型,整片晶圓透過凸塊(Bumping)與基板相連。由於省略了打線(Wire Bonding)或導線架(leadframe),訊號傳輸路徑極短,有利於高頻運算並進一步縮小封裝尺寸。晶圓級封裝(WLP)因佈線方式的不同可區分為扇入型 (Fan-In WLP)及扇出型 (Fan-Out WLP)。扇入型 (Fan-In WLP)的佈線局限在晶片尺寸內,I/O 數量有限,適用於接腳數較少的晶片。扇出型 (Fan-Out WLP)是為了因應更多接腳,透過重新分配層(RDL)將佈線向外擴展至晶片範圍外,擴大佈線範圍,實現更多 I/O 腳數。

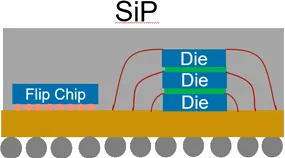

系統級封裝(System-in-Package, SiP):是一種將多個功能不同的晶片(如處理器、記憶體、感測器等)與被動元件(如電阻、電容等)等異質元件整合在同一個封裝內的技術,使其能在單一封裝體中實現完整的系統功能,達到小型化、高性能、低功耗、高整合度和縮短開發時間。

第三階段:先進封裝 (Advanced Packaging)

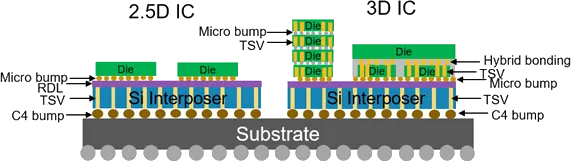

先進封裝 (Advanced Packaging) 是半導體產業為突破「摩爾定律」物理極限、持續提升晶片效能的核心技術。相較於傳統封裝僅提供機械保護與基本導電,先進封裝著重於異質整合 (Heterogeneous Integration),將不同製程、不同功能的晶片(如 CPU、GPU、記憶體)縮短間距進行整合,以達到低功耗、高頻寬與小體積的目標。目前主流技術有2.5D封裝與3D封裝。2.5D封裝如CoWoS 將系統單晶片(SoC)、記憶體等晶片設置於矽中介層(Si interposer)上,經由RDL及微凸塊(Microbumps)進行連結,讓各晶片間的電子訊號順利傳輸,並經矽中介層 (Si Interposer)及C4凸塊(C4 bump)連結至下方的基板。3D封裝採垂直堆疊晶片,垂直堆疊晶片經由微凸塊(Microbumps)或混合鍵合(Hybrid Bonding)進行晶片間的連接,並經由「矽穿孔」(TSV)及微凸塊(micro bump)連結至矽中介層(Si interposer)上。混合鍵合 (Hybrid Bonding),其「無凸塊 (Bumpless)」設計能提供前所未有的互連密度。