UBM 技術概述:用途、應用與蝕刻化學品解析

UBM技術概述:用途、應用與蝕刻化學品解析

1. 引言

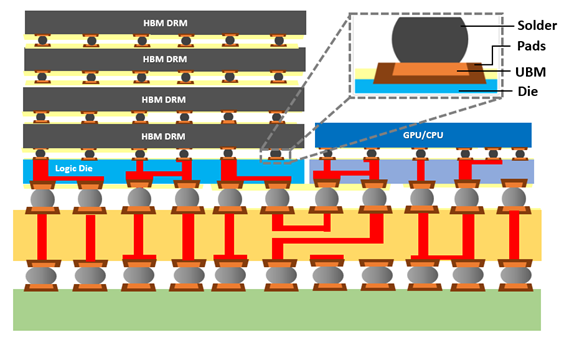

隨著半導體封裝技術向高密度、細間距(Fine Pitch)發展,先進封裝如Flip-Chip、Wafer-Level Packaging(WLP)和高階2.5D/3D封裝,對焊球下金屬層(UBM, Under Bump Metallization)的需求日益增加。UBM不僅是銅柱(Cu Pillar)或金屬焊球(Solder Bump)與晶片電路之間的導電橋樑,也提升銅柱(Cu Pillar)或金屬焊球(Solder Bump)的熱應力與機械可靠性,並在封裝良率中扮演關鍵角色。本文將說明UBM 的用途、應用、材料選擇及蝕刻化學品應用。

2. UBM 的用途與應用

2.1 主要用途

UBM是一種先進的封裝製程,主要是在半導體晶片封裝中的集成電路(IC)與銅柱(Cu Pillar)或焊球(Solder Bump)之間製造薄膜金屬層,其主要用途包括:

- 導電連接:提供電性連接橋樑,使晶片 I/O 與封裝焊球間具有低阻抗導電性。

- 潤濕層:作為焊球附著的潤濕層(Wetting Layer),確保焊球在回流焊或再流焊過程中與晶片金屬充分接合。

- 擴散阻隔層(Diffusion Barrier):防止焊球金屬(如 Sn、Ag、Cu)向晶片互連層擴散,保護晶片電路。

- 機械支撐:支撐焊球,改善熱應力及機械應力的分散,提高可靠性。

2.2 應用領域

UBM廣泛應用於多種封裝形式:

- Flip-Chip封裝:在晶片上的焊墊(Solder Pad)與後續的焊料凸塊(Solder Bump)之間形成金屬薄膜層,以提供訊號連接並阻擋焊錫擴散,確保晶片與基板的可靠連接。

- Wafer-Level Packaging (WLP):UBM提供晶圓級封裝焊球(Solder Ball)或銅柱(Cu Pillar)附著與電性連接。

- 高階3D封裝 / CoWoS / HBM 封裝:UBM 在 TSV(Through Silicon Via)或晶片堆疊中作為焊球(Solder Ball)或銅柱(Cu Pillar)與晶片層之間的金屬橋梁。

3. UBM 材質選擇

3.1 UBM 通常採多層金屬結構設計,以兼顧導電性、潤濕性與阻隔功能。典型的 UBM 層次為:

|

層次 |

常用材料 |

功能 |

| 附著層 | Ti、TiW、Ta | 改善與晶片金屬(Al 或 Cu)附著 |

| 種子層/ 導體層 | Cu | 電鍍導電層 |

| 阻擋層 | TiN, TiW, Ta, TaN | 主要用途是防止Sn/Cu擴散 |

| Barrier Layer | Ni, NiV | 阻擋 Sn 擴散至 Cu,提升焊球可靠性 |

| 濕潤層 | Au, Ag | 提供焊球附著潤濕性 |

| 錫焊層 | Sn / SnAgCu | 部分高階封裝直接在 Ni 層上沉積錫焊,改善焊球接合 |

| 附著層 / 阻擋層 | Cr | 提高附著力,阻止 Sn/Cu 擴散 |

3.2 料選擇要點

- 鎳(Ni)層厚度需均勻,過厚會增加焊球疲勞裂紋風險,過薄則失去阻隔功能。

- 金層(Au)厚度通常在 0.05~0.3 μm,過厚會增加成本,過薄易氧化。

- 黏著層需與晶片金屬相容,通常採 Ti/TiW 層壓或濺鍍工藝。

4. UBM 蝕刻化學品(UBM Etching Chemicals)

UBM 製程中常需進行選擇性蝕刻,以去除多餘金屬層並定義焊球 pad。蝕刻化學品選型取決於金屬材質:

4.1 UBM常用蝕刻化學品

|

金屬 |

蝕刻化學品 |

特性與注意事項 |

應用 |

| Ti / TiN / TiW | HF + H₂O₂;NH₄OH + H₂O₂ | 改善與晶片金屬(Al 或 Cu)附著 | 黏著/阻擋層 |

| Cu | H3PO4 + H2O2; H2SO4 + H2O2 ; HNO3 / | 電鍍導電層 | RDL、導線 |

| Ta / TaN | HF + H₂O₂;NH₄OH + H₂O₂ | 主要用途是防止Sn/Cu擴散 | Cu 阻擋層 |

| Ni / NiV | HNO₃ + HCl;FeCl₃ | 阻擋 Sn 擴散至 Cu,提升焊球可靠性 | UBM、基板保護 |

| Au | KI / I₂ 或氰化物溶液 | 提供焊球附著潤濕性 | UBM 潤濕層 |

| Cr | Ceric Ammonium Nitrate (硝酸銨銨溶液) + HNO₃ | 部分高階封裝直接在 Ni 層上沉積錫焊,改善焊球接合 | 光罩、ITO 黏著層 |

4.2 工藝控制要點

- 蝕刻速率與溫度、pH 值、金屬厚度高度相關。

- 多層 UBM 蝕刻需分段控制,避免過蝕造成焊球接合不良。

- 防護層(Resist / Photoresist)需抗蝕選擇性高,以確保 pad 定義精準。

5. 未來發展趨勢

- 細間距與高 I/O 封裝:隨著 HBM、CoWoS 及 SiP 封裝 I/O 密度提升,UBM 需支援 <50 μm pad pitch,對材料均勻性與蝕刻精準度要求更高。

- 環保與低成本材料:探索替代 Au 層、減少貴金屬使用,同時保持焊球附著性與可靠性。

- 乾蝕刻與等離子體蝕刻:相較於濕蝕刻,可降低廢液排放,並提升蝕刻精度與選擇性。

6. 結論

UBM作為晶片電路(IC)與銅柱(Cu Pillar)或焊球(Solder Bump)之間的橋梁,其設計與製程直接影響半導體封裝之可靠性與良率。材料選擇、層次設計以及蝕刻化學品的精準應用是技術核心。隨著高密度封裝需求增長,UBM 技術將持續向高可靠性、環保與低成本方向演進。