UBM Technical Overview: Applications, Uses, and Etching Chemicals

UBM Technical Overview: Applications, Uses, and Etching Chemicals

1. Introduction

The semiconductor industry is undergoing a profound transformation as devices demand higher performance, smaller form factors, and lower power consumption. Traditional packaging approaches are no longer sufficient to meet the requirements of AI accelerators, high-performance computing (HPC), 5G communication, autonomous vehicles, and consumer electronics, all of which rely heavily on advanced packaging technologies to enable higher bandwidth, greater interconnect density, and improved thermal management.

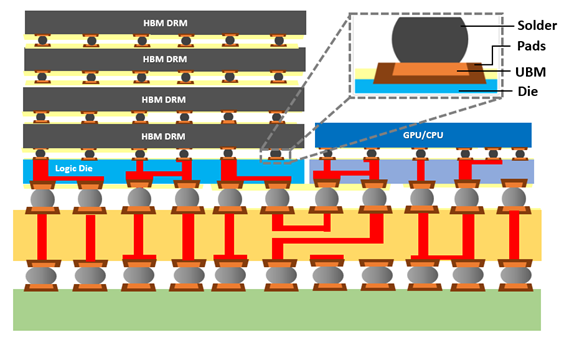

As the industry continues to shift towards high density, fine pitch interconnections, packaging methods such as Flip-Chip, Wafer-Level Packaging (WLP), Fan-Out WLP, 2.5D interposers, and 3D IC stacking have gained significant momentum. These approaches allow for shorter interconnect paths, reduced parasitic losses, and increased I/O density—critical for supporting today’s data-driven applications.

At the heart of these technologies lies Under Bump Metallization (UBM), a key enabler for forming reliable electrical and mechanical connections between the chip and the external world. UBM is far more than a passive layer; it provides adhesion, electrical conductivity, mechanical stability, and barrier properties essential for the long-term reliability of the device. By ensuring robust bonding between copper pillars (Cu pillars) or solder bumps and the underlying chip circuitry, UBM directly impacts yield, performance, and product lifetime.

As advanced nodes and packaging technologies push the boundaries of integration, the role of UBM has become increasingly critical. Without a properly engineered UBM stack, challenges such as delamination, solder voiding, electromigration, and thermal stress failures would compromise the viability of high-end packages. Thus, UBM stands as a foundation for next-generation semiconductor reliability and manufacturability.

This document explains in detail the purpose, applications, material choices, etching chemistry, and future trends in UBM technology, highlighting its indispensable role in the evolution of advanced packaging.

2. Functions and Applications of UBM

2.1 Primary Functions

UBM is an advanced packaging process that creates a thin metal layer between the integrated circuit (IC) and Cu Pillar or solder bump in semiconductor packaging. Its main functions include:

Electrical Interconnection

UBM forms the critical conductive pathway between the chip’s I/O pads (typically aluminum or copper) and the external package bumps (solder or Cu pillars).

- The seed layer within the UBM stack enables electroplating of solder or Cu pillars, ensuring uniform deposition.

- By providing a low-impedance and stable current path, UBM minimizes resistive losses and supports high-frequency signal integrity.

- Properly engineered UBM also reduces risks of electromigration, current crowding, and joule heating, which are critical failure modes in fine-pitch interconnects.

Wetting Layer

The upper surface of UBM is engineered to promote excellent solder wettability and adhesion during reflow.

- Noble metals such as Au, Pd, or Ni(P) are often used to create a surface that resists oxidation and ensures consistent solder spreading.

- This function is crucial to avoid non-wetting defects, voids, or irregular bump shapes, all of which can compromise yield and reliability.

- In Cu pillar technology, the wetting layer ensures uniform solder capping and prevents incomplete or non-uniform joint formation.

Diffusion Barrier

UBM incorporates barrier materials (e.g., TiW, Ta, WNx, Ni) that prevent unwanted atomic migration between solder, Cu pillars, and the IC metallization.

- Prevents upward diffusion: Stops Cu or Al from migrating into the solder, which could cause brittle intermetallic compounds (IMCs) or electrical leakage.

- Prevents downward diffusion: Stops Sn, Ag, or Pb from penetrating into the chip circuitry, which could weaken the device structure or cause shorts.

- This barrier function is critical to maintain chemical stability of the interconnect, especially under high temperature and long-term operation.

Mechanical Support

UBM plays a dual role in mechanical reinforcement and stress distribution:

- Provides structural anchoring for solder bumps or Cu pillars, preventing pad lift-off or bump detachment.

- Distributes thermo-mechanical stresses caused by coefficient of thermal expansion (CTE) mismatch between silicon, solder, and substrate materials.

- Enhances fatigue resistance during repeated thermal cycling, ensuring long-term package reliability.

- Serves as a stress buffer at the critical interface, reducing crack propagation, delamination, and bump failure in high-density packaging.

2.2 Application Fields

UBM is widely used in multiple packaging formats:

• Flip-Chip Packaging: A thin metallic film layer formed between chip pads and solder bumps to ensure reliable electrical connections and prevent solder diffusion.

• Wafer-Level Packaging (WLP): Provides adhesion and electrical connection for solder balls or Cu Pillars at wafer level.

• High-end 3D Packaging / CoWoS / HBM: Functions as a metal bridge in TSVs (Through-Silicon Vias) or chip stacking, ensuring robust interlayer connections.

3. UBM Material Selection

3.1 Typical Multi-Layer Structure

|

Layer Type |

Common Materials |

Function |

|---|---|---|

| Adhesion Layer | Ti, TiW, Ta | Enhances adhesion with Al or Cu chip metals |

| Seed/Conductor Layer | Cu | Provides plating conduction |

| Barrier Layer | TiN, TiW, Ta, TaN | Prevents Sn/Cu diffusion |

| Barrier Layer | Ni, NiV | Blocks Sn diffusion into Cu, improves solder bump reliability |

| Wetting Layer | Au, Ag | Ensures solder wettability |

| Solder Layer | Sn / SnAgCu | Directly deposited on Ni for better solder bonding |

| Adhesion/Barrier Layer | Cr | Improves adhesion and blocks Sn/Cu diffusion |

3.2 Material Considerations

• Ni thickness must be uniform: too thick increases solder fatigue cracking risk, too thin loses barrier function.

• Au thickness is typically 0.05–0.3 μm: too thick raises costs, too thin is prone to oxidation.

• Adhesion layers should be compatible with chip metals, often deposited by sputtering.

4. UBM Etching Chemicals

UBM processes often require selective etching to remove excess metal and define solder pads. The choice of etchant depends on the metal used.

4.1 Common Etchants

4.2 Process Control Points

• Etch rate depends on temperature, pH, and metal thickness.

• Multi-layer UBM requires staged etching to avoid over-etching.

• Resist must have high selectivity to ensure pad definition accuracy.

5. Future Trends

• Fine Pitch & High I/O Packaging: With HBM, CoWoS, and SiP pushing <50 μm pad pitch, UBM demands higher uniformity and precise etching.

• Eco-Friendly & Cost Reduction: Research into alternatives to Au layers to reduce precious metal usage while retaining solder adhesion and reliability.

• Dry/Plasma Etching: Compared with wet etching, plasma reduces waste liquid discharge and improves etch accuracy but difficult to control the aspect ratio and uniformity.

6. Conclusion

Under Bump Metallization (UBM) is a critical enabler of advanced semiconductor packaging, ensuring reliable electrical and mechanical connections between IC circuitry and Cu pillars or solder bumps. The choice of materials, structural design, and precise control of etching processes are fundamental in determining overall packaging reliability, yield, and performance.

As the industry moves towards higher I/O density, finer pitches, and more complex integration schemes, the role of UBM becomes even more significant. Future developments will focus on enhancing reliability, process scalability, eco-friendly chemistries, and cost efficiency, aligning with the demands of next-generation applications such as AI, 5G, and high-performance computing.

In essence, UBM is more than a metallization layer; it is a foundation for innovation in semiconductor packaging, bridging today’s requirements with tomorrow’s technological possibilities.

If you have any further questions, please feel free to contact us by using Line or Email.

E-mail: info@scientech.com.tw

All the best!